This article presents a triple redundant on-chip interconnect bus that provides low-speed peripherals with high reliability. In addition to correcting single errors and detecting duplicated ones, the proposed circuit offers zero latency and is transparent for both the embedded processor and the peripherals. These characteristics make it suitable for hard real-time applications. At the same time, the impact on area and power consumption is minimal.

Enhancing electronic systems safety

AXI Lite Redundant On-Chip Bus Interconnect for High Reliability Systems

A new contribution released in Open Access format by APERT research team

First publication date: 18/10/2022

(Opens New Window)

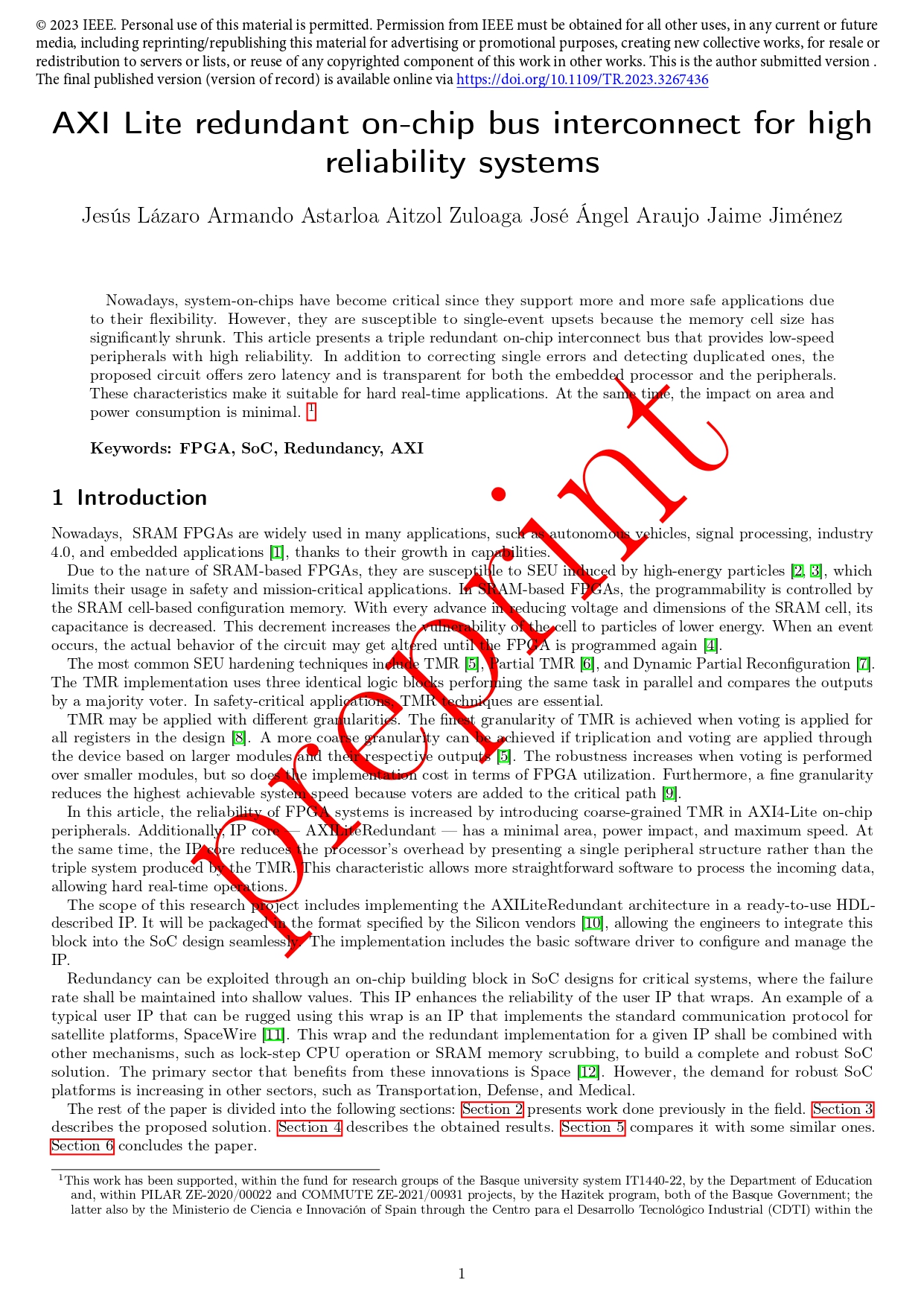

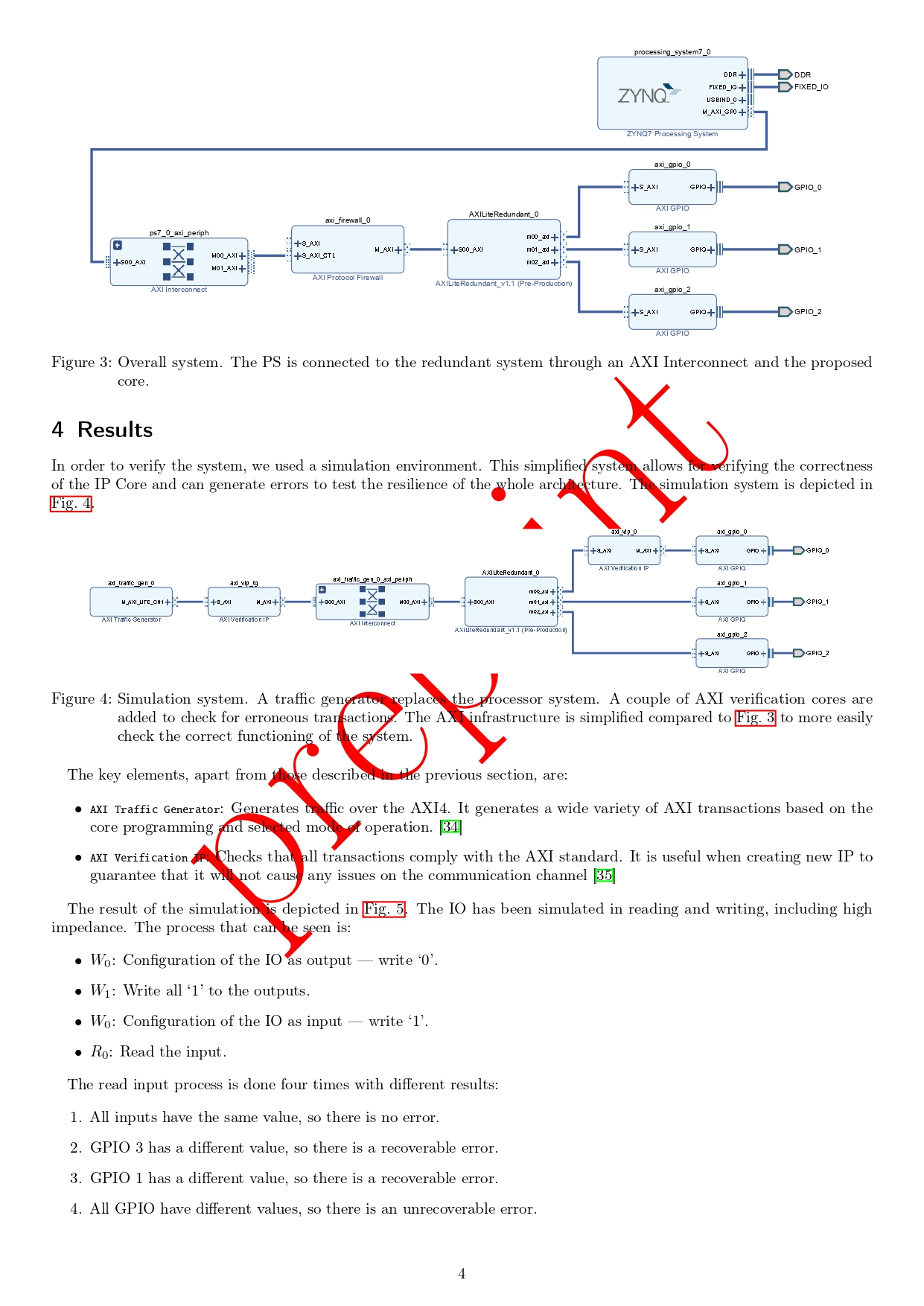

Nowadays, system-on-chips have become critical since they support more and more safe applications due to their flexibility. However, they are susceptible to single-event upsets because the memory cell size has significantly shrunk. This article presents a triple redundant on-chip interconnect bus that provides low-speed peripherals with high reliability. In addition to correcting single errors and detecting duplicated ones, the proposed circuit offers zero latency and is transparent for both the embedded processor and the peripherals. These characteristics make it suitable for hard real-time applications. At the same time, the impact on area and power consumption is minimal.

Bibliographic reference

- AXI Lite redundant on-chip bus interconnect for high reliability systems

- IEEE Transactions on Reliability, 2023

- DOI: https://doi.org/10.1109/TR.2023.3267436